Product Summary

The EM638165TS-7 is a high-speed CMOS synchronous DRAM. It is internally configured as 4 Banks of 1M word x 16 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of a BankActivate command which is then followed by a Read or Write command.

Parametrics

EM638165TS-7 absolute maximum ratings: (1)Voltage on any pin relative to VSS (Vin, Vout ): -1.0V to +4.6V; (2)Voltage on VDD supply relative to VSS (VDD, VDDQ ): -1.0V to +4.6V; (3)Operating Temperature(TOPR): 0℃ to +70℃; (4)Storage Temperature (TSTG): -55℃ to +125℃; (5)Power Dissipation (PD): 1W; (6)Short Circuit Output Current (Iout): 50mA.

Features

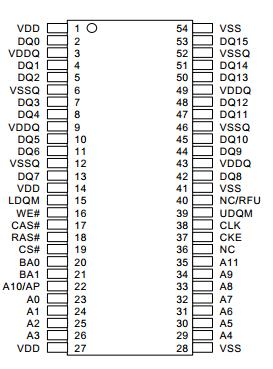

EM638165TS-7 features: (1)Fast access time from clock: 5/6/6/6/7 ns; (2)Fast clock rate: 166/143/133/125/100 MHz; (3)Fully synchronous operation; (4)Internal pipelined architecture; (5)1M word × 16-bit × 4-bank; (6)Auto Refresh and Self Refresh; (7)4096 refresh cycles/64ms; (8)CKE power down mode; (9)Single +3.3V ± 0.3V power supply; (10)Interface: LVTTL; (11)54-pin 400 mil plastic TSOP II package.

Diagrams

(China (Mainland))

(China (Mainland))