Product Summary

The MT48LC8M16A2TG-7EB is a 128Mb SDRAM. The MT48LC8M16A2TG-7EB is a high-speed CMOS, dynamic random-access memory containing 134,217,728 bits. It is internally configured as a quad-bank DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the x4s 33,554,432-bit banks is organized as 4,096 rows by 2,048 columns by 4 bits.The MT48LC8M16A2TG-7EB is designed to operate in 3.3V memory systems. An auto refresh mode is provided, along with a power-saving, power-down mode. All inputs and outputs are LVTTL-compatible. SDRAMs offer substantial advances in DRAM operating performance, including the ability to synchronously burst data at a high data rate with automatic columnaddress generation, the ability to interleave between internal banks in order to hide precharge time and the capability to randomly change column addresses on each clock cycle during a burst access.

Parametrics

MT48LC8M16A2TG-7EB absolute maximum ratings: (1)Voltage on VDD/VDDQ Supply Relative to VSS : -1V to +4.6V; (2)Voltage on Inputs, NC or I/O Pins Relative to VSS : -1V to +4.6V; (3)Operating Temperature, TA (commercial): 0°C to +70°C; (4)Operating Temperature, TA (extended; IT parts): -40°C to +85°C; (5)Storage Temperature (plastic): -55°C to +150°C; (6)Power Dissipation: 1W.

Features

MT48LC8M16A2TG-7EB features: (1)PC100-, and PC133-compliant; (2)Fully synchronous; all signals registered on positive edge of system clock; (3)Internal pipelined operation; column address can be changed every clock cycle; (4)Internal banks for hiding row access/precharge; (5)Programmable burst lengths: 1, 2, 4, 8, or full page; (6)Auto Precharge, includes CONCURRENT AUTO PRECHARGE, and Auto Refresh Modes; (7)Self Refresh Mode; standard and low power; (8)64ms, 4,096-cycle refresh; (9)LVTTL-compatible inputs and outputs; (10)Single +3.3V ±0.3V power supply.

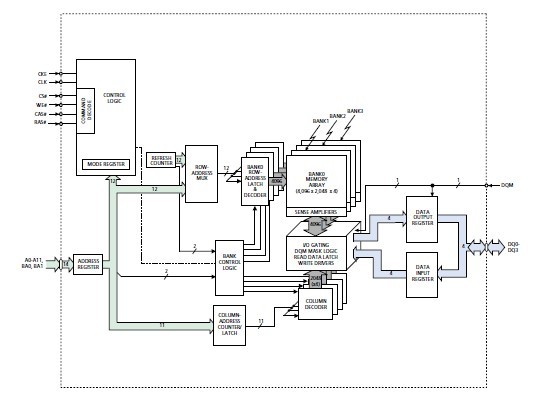

Diagrams

(China (Mainland))

(China (Mainland))