Product Summary

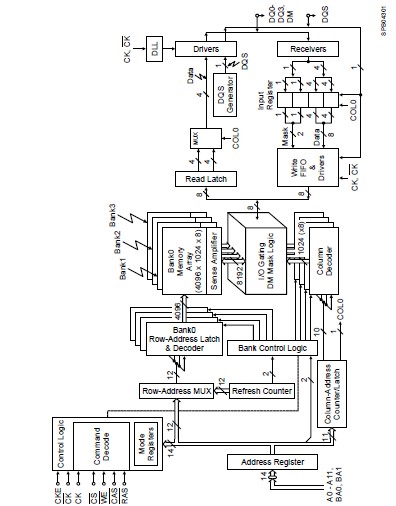

The HYB25D128160CE-6 is a 128 Mbit double data rate SDRAM. It is a high-speed CMOS, dynamic random-access memory containing 268,435,456 bits. The HYB25D128160CE-6 is internally configured as a quad-bank DRAM. The HYB25D128160CE-6 uses a double-data-rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2n prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the HYB25D128160CE-6 effectively consists of a single 2n-bit wide, one clock cycle data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins. A bidirectional data strobe (DQS) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the HYB25D128160CE-6 during Reads and by the memory controller during Writes. DQS is edge-aligned with data for Reads and center-aligned with data for Writes. The HYB25D128160CE-6 operates from a differential clock (CK and CK; the crossing of CK going HIGH and CK going LOW is referred to as the positive edge of CK). Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK.

Parametrics

HYB25D128160CE-6 absolute maximum ratings: (1)Voltage on I/O pins relative to VSS VIN, VOUT: –0.5 to VDDQ +0.5 V; (2)Voltage on inputs relative to VSS VIN: –1 to +3.6 V; (3)Voltage on VDD supply relative to VSS VDD: –1 to +3.6 V; (4)Voltage on VDDQ supply relative to VSS VDDQ: –1 to +3.6 V; (5)Operating temperature (ambient)TA: 0 to +70 °C; (6)Storage temperature (plastic)TSTG: -55 to +150 °C; (7)Power dissipation (per SDRAM component)PD: 1.5 W; (8)Short circuit output current IOUT: 50 mA.

Features

HYB25D128160CE-6 features: (1)Double data rate architecture: two data transfers per clock cycle; (2)Bidirectional data strobe (DQS)is transmitted and received with data, to be used in capturing data at the receiver; (3)DQS is edge-aligned with data for reads and is center-aligned with data for writes; (4)Differential clock inputs; (5)Four internal banks for concurrent operation; (6)Data mask (DM)for write data; (7)DLL aligns DQ and DQS transitions with CK transitions; (8)Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS; (9)Burst Lengths: 2, 4, or 8; (10)CAS Latency: 2, 2.5, 3; (11)Auto Precharge option for each burst access; (12)Auto Refresh and Self Refresh Modes; (13)7.8μs Maximum Average Periodic Refresh Interval; (14)2.5 V (SSTL_2 compatible)I/O; (15)VDDQ = 2.5 V ± 0.2 V (DDR266A, DDR333); VDDQ = 2.6 V ± 0.1 V (DDR400); (16)VDD = 2.5 V ± 0.2 V (DDR266, DDR333); VDD = 2.6 V ± 0.1 V (DDR400); (17)P-TFBGA-60-2 package with 3 depopulated rows (12 × 8 mm2); (18)P-TSOPII-66-1 package; (19)Lead- and halogene-free = green product.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

HYB25D128160CE-6 |

Other |

|

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

HYB25D128 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB25D128160AL |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB25D128160AT |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB25D128160CE-5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB25D128160CE-6 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB25D128160CT-6 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))